# **CMT2119A**

## 240 – 960 MHz (G)FSK/OOK Transmitter

#### **Features**

- Optional Chip Feature Configuration Schemes

- · On-Line Registers Configuration

- Off-Line EEPROM Programming

- Frequency Range: 240 to 960 MHz

- FSK, GFSK and OOK Modulation

- Symbol Rate:

- 0.5 to 100 ksps (FSK/GFSK)

- 0.5 to 30 ksps (OOK)

- Deviation: 1.0 to 200 kHz

- Two-wire Interface for Registers Accessing and EEPROM Programming

- Output Power: -10 to +13 dBmSupply Voltage: 1.8 to 3.6 V

- Sleep Current: < 20 nA</li>FCC/ETSI Compliant

- RoHS Compliant

- 6-pin SOT23-6 Package

### **Applications**

- Low-Cost Consumer Electronics Applications

- Home and Building Automation

- Remote Fan Controllers

- Infrared Transmitter Replacements

- Industrial Monitoring and Controls

- Remote Lighting Control

- Wireless Alarm and Security Systems

- Remote Keyless Entry (RKE)

## **Ordering Information**

| Part Number        | Frequency  | Package | MOQ       |

|--------------------|------------|---------|-----------|

| CMT2119A-ESR       | 868.35 MHz | SOT23-6 | 3,000 pcs |

| More Ordering Info |            |         |           |

## **Descriptions**

The CMT2119A is a high performance, highly flexible, low-cost, single-chip (G)FSK/OOK transmitter for various 240 to 960 MHz wireless applications. It is a part of the CMOSTEK NextGenRF<sup>TM</sup> family, which includes a complete line of transmitters, receivers and transceivers. The CMT2119A provides the simplest way to control the data transmission. The transmission is started when an effective level turnover is detected on the DATA pin, while the transmission action will stop after the DATA pin holding level low for a defined time window, or after a two-wire interface (TWI) command is issued. The chip features can be configured in two different ways: setting the configuration registers through the TWI, or programming the embedded EEPROM with CMOSTEK USB Programmer and the RFPDK. The device operates from a supply voltage of 1.8 V to 3.6 V, consumes 27.6 mA (FSK @ 868.35 MHz) when transmitting +10 dBm output power, and only leak 20 nA when it is in sleep state. The CMT2119A transmitter together with the CMT2219A receiver enables a robust RF link.

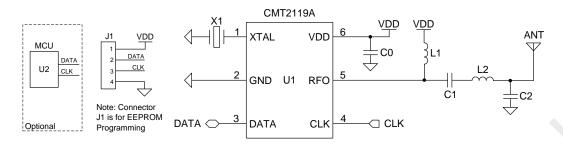

## **Typical Application**

Figure 1. CMT2119A Typical Application Schematic

Table 1. BOM of 433.92/868.35 MHz Low-Cost Application

| Business   | B. a.       | Valu                  | ue  |      |              |

|------------|-------------------------------------------------|-----------------------|-----|------|--------------|

| Designator | Descriptions                                    | 433.92 MHz 868.35 MHz |     | Unit | Manufacturer |

| U1         | CMT2119A, 240 – 960 MHz (G)FSK/OOK transmitter  | (                     |     | -    | CMOSTEK      |

| U2         | Optional MCU for on-line register configuration |                       |     | -    | -            |

| X1         | ±20 ppm, SMD32*25 mm crystal                    | 2                     | 6   | MHz  | EPSON        |

| C0         | ±20%, 0402 X7R, 25 V                            | 0                     | .1  | uF   | Murata GRM15 |

| C1         | ±5%, 0402 NP0, 50 V                             | 82                    | 82  | pF   | Murata GRM15 |

| C2         | ±5%, 0402 NP0, 50 V                             | 9                     | 3.9 | pF   | Murata GRM15 |

| L1         | ±5%, 0603 multi-layer chip inductor             | 180                   | 100 | nΗ   | Murata LQG18 |

| L2         | ±5%, 0603 multi-layer chip inductor             | 27                    | 8.2 | nΗ   | Murata LQG18 |

### **Abbreviations**

Abbreviations used in this data sheet are described below

| AN            | Application Notes                            | PA      | Power Amplifier                     |

|---------------|----------------------------------------------|---------|-------------------------------------|

| BOM           | Bill of Materials                            | PC      | Personal Computer                   |

| BSC           | Basic Spacing between Centers                | PCB     | Printed Circuit Board               |

| <b>EEPROM</b> | Electrically Erasable Programmable Read-Only | PN      | Phase Noise                         |

|               | Memory                                       | RCLK    | Reference Clock                     |

| ESD           | Electro-Static Discharge                     | RF      | Radio Frequency                     |

| ESR           | Equivalent Series Resistance                 | RFPDK   | RF Product Development Kit          |

| ETSI          | European Telecommunications Standards        | RoHS    | Restriction of Hazardous Substances |

|               | Institute                                    | Rx      | Receiving, Receiver                 |

| FCC           | Federal Communications Commission            | SOT     | Small-Outline Transistor            |

| FSK           | Frequency Shift Keying                       | SR      | Symbol Rate                         |

| GFSK          | Gauss Frequency Shift Keying                 | TWI     | Two-wire Interface                  |

| Max           | Maximum                                      | Tx      | Transmission, Transmitter           |

| MCU           | Microcontroller Unit                         | Тур     | Typical                             |

| Min           | Minimum                                      | USB     | Universal Serial Bus                |

| MOQ           | Minimum Order Quantity                       | XO/XOSC | Crystal Oscillator                  |

| NP0           | Negative-Positive-Zero                       | XTAL    | Crystal                             |

| OBW           | Occupied Bandwidth                           | PA      | Power Amplifier                     |

| оок           | On-Off Keying                                |         |                                     |

### **Table of Contents**

| 1. | . Electrical Characteristics                         | 5  |

|----|------------------------------------------------------|----|

|    | 1.1 Recommended Operating Conditions                 | 5  |

|    | 1.2 Absolute Maximum Ratings                         | 5  |

|    | 1.3 Transmitter Specifications                       | 6  |

|    | 1.4 Crystal Oscillator                               | 7  |

| 2. | . Pin Descriptions                                   | 8  |

|    | . Typical Performance Characteristics                |    |

| 4. | . Typical Application Schematics                     | 10 |

|    | 4.1 Low-Cost Application Schematic                   | 10 |

|    | 4.2 FCC/ETSI Compliant Application Schematic         |    |

| 5. | . Functional Descriptions                            | 12 |

|    | 5.1 Overview                                         | 12 |

|    | 5.2 Modulation, Frequency, Deviation and Symbol Rate | 12 |

|    | 5.3 Embedded EEPROM and RFPDK                        |    |

|    | 5.4 On-line Register Configuration                   |    |

|    | 5.5 Power Amplifier                                  |    |

|    | 5.6 PA Ramping                                       | 15 |

|    | 5.7 Crystal Oscillator and RCLK                      | 15 |

| 6. | . Working States and Transmission Control Interface  | 17 |

|    | 6.1 Working States                                   | 17 |

|    | 6.2 Transmission Control Interface                   | 17 |

|    | 6.2.1 Tx Enabled by DATA Pin Rising Edge             |    |

|    | 6.2.2 Tx Enabled by DATA Pin Falling Edge            |    |

|    | 6.2.3 Two-wire Interface                             |    |

| 7. | On-Line Register Configuration Flow                  | 21 |

|    | 7.1 Accessing Registers with TWI                     | 21 |

|    | 7.2 Configuration Flow                               | 22 |

| 8. | Ordering Information                                 | 24 |

| 9. | Package Outline                                      | 25 |

| 10 | 0. Top Marking                                       | 26 |

|    | 10.1 CMT2119A Top Marking                            | 26 |

| 11 | 1. Other Documentations                              | 27 |

|    | 2. Document Change List                              |    |

| 13 | 3. Contact Information                               | 29 |

#### 1. Electrical Characteristics

$V_{DD}$  = 3.3 V,  $T_{OP}$  = 25  $^{\circ}$ C,  $F_{RF}$  = 868.35 MHz, FSK modulation, output power is +10 dBm terminated in a matched 50  $\Omega$  impedance, unless otherwise noted.

#### 1.1 Recommended Operating Conditions

**Table 2. Recommended Operation Conditions**

| Parameter                | Symbol          | Conditions | Min | Тур | Max | Unit       |

|--------------------------|-----------------|------------|-----|-----|-----|------------|

| Operation Voltage Supply | $V_{DD}$        |            | 1.8 |     | 3.6 | V          |

| Operation Temperature    | T <sub>OP</sub> |            | -40 |     | 85  | $^{\circ}$ |

| Supply Voltage Slew Rate |                 |            | 1   |     |     | mV/us      |

### 1.2 Absolute Maximum Ratings

Table 3. Absolute Maximum Ratings<sup>[1]</sup>

| Parameter             | Symbol           | Conditions                | Min  | Max                   | Unit                 |

|-----------------------|------------------|---------------------------|------|-----------------------|----------------------|

| Supply Voltage        | $V_{DD}$         |                           | -0.3 | 3.6                   | V                    |

| Interface Voltage     | V <sub>IN</sub>  |                           | -0.3 | V <sub>DD</sub> + 0.3 | V                    |

| Junction Temperature  | TJ               |                           | -40  | 125                   | $^{\circ}$ C         |

| Storage Temperature   | T <sub>STG</sub> |                           | -50  | 150                   | $^{\circ}$ C         |

| Soldering Temperature | T <sub>SDR</sub> | Lasts at least 30 seconds |      | 255                   | $^{\circ}\mathbb{C}$ |

| ESD Rating            |                  | Human Body Model (HBM)    | -2   | 2                     | kV                   |

| Latch-up Current      |                  | @ 85 °C                   | -100 | 100                   | mA                   |

#### Note:

[1]. Stresses above those listed as "absolute maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device under these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

**Caution!** ESD sensitive device. Precaution should be used when handling the device in order to prevent permanent damage.

### 1.3 Transmitter Specifications

**Table 4. Transmitter Specifications**

| Parameter                          | Symbol                | Conditions                                                   | Min | Тур  | Max  | Unit     |

|------------------------------------|-----------------------|--------------------------------------------------------------|-----|------|------|----------|

| Frequency Range <sup>[1]</sup>     | $F_RF$                |                                                              | 240 |      | 960  | MHz      |

| Synthesizer Frequency              | _                     | F <sub>RF</sub> ≤ 480 MHz                                    |     | 198  |      | Hz       |

| Resolution                         | F <sub>RES</sub>      | F <sub>RF</sub> > 480 MHz                                    |     | 397  |      | Hz       |

| 0 1 15 /                           | 0.0                   | FSK/GFSK                                                     | 0.5 |      | 100  | ksps     |

| Symbol Rate                        | SR                    | ООК                                                          | 0.5 |      | 30   | ksps     |

| (G)FSK Modulation Deviation Range  | F <sub>DEV</sub>      |                                                              | 1   |      | 200  | kHz      |

| Bandwidth-Time Product             | ВТ                    | GFSK modulation                                              | -   | 0.5  | -    | <u> </u> |

| Maximum Output Power               | P <sub>OUT(Max)</sub> |                                                              |     | +13  |      | dBm      |

| Minimum Output Power               | P <sub>OUT(Min)</sub> |                                                              |     | -10  |      | dBm      |

| Output Power Step Size             | P <sub>STEP</sub>     |                                                              |     | 1    |      | dB       |

| OOK PA Ramping Time <sup>[2]</sup> | t <sub>RAMP</sub>     |                                                              | 0   |      | 1024 | us       |

|                                    |                       | OOK, 0 dBm, 50% duty cycle                                   |     | 6.7  |      | mA       |

|                                    |                       | OOK, +10 dBm, 50% duty cycle                                 |     | 13.4 |      | mA       |

| Current Consumption                |                       | OOK, +13 dBm, 50% duty cycle                                 |     | 17.4 |      | mA       |

| @ 433.92 MHz                       | DD-433.92             | FSK, 0 dBm, 9.6 ksps                                         |     | 10.5 |      | mA       |

|                                    |                       | FSK, +10 dBm, 9.6 ksps                                       |     | 23.5 |      | mA       |

|                                    |                       | FSK, +13 dBm, 9.6 ksps                                       |     | 32.5 |      | mA       |

|                                    |                       | OOK, 0 dBm, 50% duty cycle                                   |     | 8.0  |      | mA       |

|                                    |                       | OOK, +10 dBm, 50% duty cycle                                 |     | 15.5 |      | mA       |

| Current Consumption                |                       | OOK, +13 dBm, 50% duty cycle                                 |     | 19.9 |      | mA       |

| @ 868.35 MHz                       | DD-868.35             | FSK, 0 dBm, 9.6 ksps                                         |     | 12.3 |      | mA       |

|                                    |                       | FSK, +10 dBm, 9.6 ksps                                       |     | 27.6 |      | mA       |

|                                    |                       | FSK, +13 dBm, 9.6 ksps                                       |     | 36.1 |      | mA       |

| Sleep Current                      | I <sub>SLEEP</sub>    |                                                              |     | 20   |      | nA       |

| Frequency Tune Time                | t <sub>TUNE</sub>     |                                                              |     | 370  |      | us       |

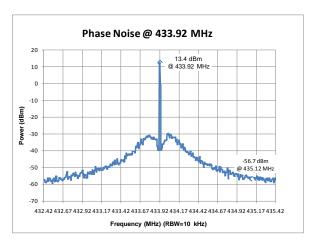

|                                    |                       | 100 kHz offset from F <sub>RF</sub>                          |     | -80  |      | dBc/Hz   |

| Phase Noise @ 433.92               | PN <sub>433.92</sub>  | 600 kHz offset from F <sub>RF</sub>                          |     | -98  |      | dBc/Hz   |

| MHz                                |                       | 1.2 MHz offset from F <sub>RF</sub>                          |     | -107 |      | dBc/Hz   |

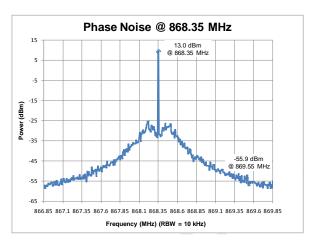

|                                    |                       | 100 kHz offset from F <sub>RF</sub>                          |     | -74  |      | dBc/Hz   |

| Phase Noise @ 868.35               | PN <sub>868.35</sub>  | 600 kHz offset from F <sub>RF</sub>                          |     | -92  |      | dBc/Hz   |

| MHz                                |                       | 1.2 MHz offset from F <sub>RF</sub>                          |     | -101 |      | dBc/Hz   |

| Harmonics Output for               | H2 <sub>433.92</sub>  | 2 <sup>nd</sup> harm @ 867.84 MHz, +13 dBm P <sub>OUT</sub>  |     | -52  |      | dBm      |

| 433.92 MHz <sup>[3]</sup>          | H3 <sub>433.92</sub>  | 3 <sup>rd</sup> harm @ 1301.76 MHz, +13 dBm P <sub>OUT</sub> |     | -60  |      | dBm      |

| Harmonics Output for               | H2 <sub>868.35</sub>  | 2 <sup>nd</sup> harm @ 1736.7 MHz, +13 dBm P <sub>OUT</sub>  |     | -67  |      | dBm      |

| 868.35 MHz <sup>[3]</sup>          | H3 <sub>868.35</sub>  | 3 <sup>rd</sup> harm @ 2605.05 MHz, +13 dBm P <sub>OUT</sub> |     | -55  |      | dBm      |

| OOK Extinction Ration              |                       |                                                              |     | 60   |      | dB       |

#### Notes

- [1]. The frequency range is continuous over the specified range.

- [2]. 0 and  $2^n$  us, n = 0 to 10, when set to "0", the PA output power will ramp to its configured value in the shortest possible

- [3]. The harmonics output is measured with the application shown as Figure 10.

### 1.4 Crystal Oscillator

**Table 5. Crystal Oscillator Specifications**

| Parameter                        | Symbol            | Conditions | Min | Тур | Max | Unit |

|----------------------------------|-------------------|------------|-----|-----|-----|------|

| Crystal Frequency <sup>[1]</sup> | F <sub>XTAL</sub> |            | 26  | 26  | 26  | MHz  |

| Crystal Tolerance <sup>[2]</sup> |                   |            |     | ±20 |     | ppm  |

| Load Capacitance <sup>[3]</sup>  | C <sub>LOAD</sub> |            | 12  |     | 20  | pF   |

| Crystal ESR                      | Rm                |            |     |     | 60  | Ω    |

| XTAL Startup Time <sup>[4]</sup> | t <sub>XTAL</sub> |            |     | 400 |     | us   |

#### Notes:

- [1]. The CMT2119A can directly work with external 26 MHz reference clock input to XTAL pin (a coupling capacitor is required) with amplitude 0.3 to 0.7 Vpp.

- [2]. This is the total tolerance including (1) initial tolerance, (2) crystal loading, (3) aging, and (4) temperature dependence. The acceptable crystal tolerance depends on RF frequency and channel spacing/bandwidth.

- [3]. The required crystal load capacitance is integrated on-chip to minimize the number of external components.

- [4]. This parameter is to a large degree crystal dependent.

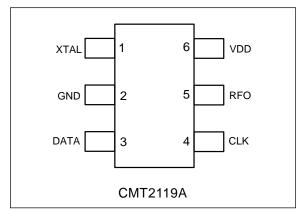

## 2. Pin Descriptions

Figure 2. CMT2119A Pin Assignments

Table 6. CMT2119A Pin Descriptions

| Pin Number | Name | I/O | Descriptions                                                                                                                                                                                                                                                                                                  |

|------------|------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | XTAL | I   | 26 MHz single-ended crystal oscillator input or External 26 MHz reference clock input                                                                                                                                                                                                                         |

| 2          | GND  | I   | Ground                                                                                                                                                                                                                                                                                                        |

| 3          | DATA | Ю   | Data input to be transmitted or Data pin to access the embedded EEPROM Pulled down internally to GND when configured as Transmission Enabled by DATA Pin Falling Edge and used as input pin Pulled up internally to VDD when configured as Transmission Enabled by DATA Pin Rising Edge and used as input pin |

| 4          | CLK  | ı   | Clock pin to control the device Clock pin to access the embedded EEPROM Pulled up internally to VDD                                                                                                                                                                                                           |

| 5          | RFO  | 0   | Power amplifier output                                                                                                                                                                                                                                                                                        |

| 6          | VDD  | I   | Power supply input                                                                                                                                                                                                                                                                                            |

### 3. Typical Performance Characteristics

Figure 3. Phase Noise,  $F_{RF} = 433.92$  MHz,  $P_{OUT} = +13$  dBm, Unmodulated

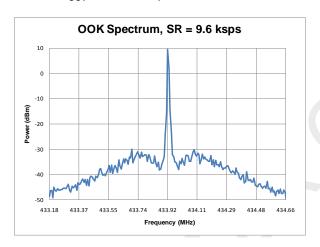

Figure 5. OOK Spectrum, SR = 9.6 ksps,  $P_{\text{OUT}} = +10 \text{ dBm}, t_{\text{RAMP}} = 32 \text{ us}$

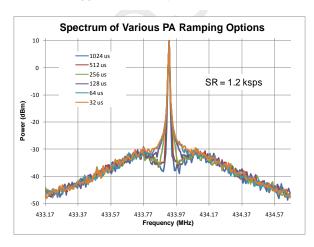

Figure 7. Spectrum of PA Ramping,  $SR = 1.2 \text{ ksps}, P_{OUT} = +10 \text{ dBm}$

Figure 4. Phase Noise,  $F_{RF}$  = 868.35 MHz,  $P_{OUT}$  = +13 dBm, Unmodulated

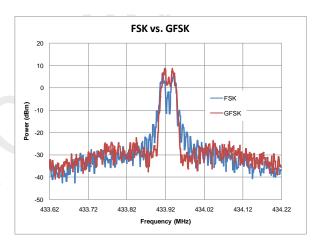

Figure 6. FSK/GFSK Spectrum,  $SR = 9.6 \text{ ksps}, F_{DEV} = 15 \text{ kHz}$

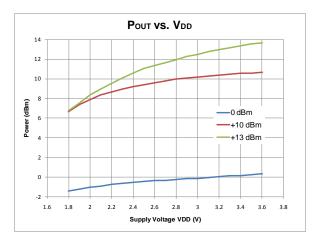

Figure 8. Output Power vs. Supply Voltages,  $F_{RF} = 433.92 \text{ MHz}$

### 4. Typical Application Schematics

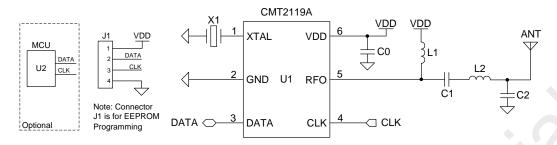

### 4.1 Low-Cost Application Schematic

Figure 9. Low-Cost Application Schematic

#### Notes:

- 1. Connector J1 is a must for the CMT2119A EEPROM access during development or manufacture.

- 2. An external MCU U2 is necessary if on-line register configuration is required.

- 3. The general layout guidelines are listed below. For more design details, please refer to "AN101 CMT211xA Schematic and PCB Layout Design Guideline"

- Use as much continuous ground plane metallization as possible.

- Use as many grounding vias (especially near to the GND pins) as possible to minimize series parasitic inductance between the ground pour and the GND pins.

- Avoid using long and/or thin transmission lines to connect the components.

- Avoid placing the nearby inductors in the same orientation to reduce the coupling between them.

- Place C0 as close to the CMT2119A as possible for better filtering.

- 4. The table below shows the BOM of 433.92/868.35 MHz Low-Cost Applications. For the BOM of 315/915 MHz application, please refer to "AN101 CMT211xA Schematic and PCB Layout Design Guideline".

Table 7. BOM of 433.92/868.35 MHz Low-Cost Application

| D i        | D. William                                      | Valu                  | ıe  | 11:4 |              |  |

|------------|-------------------------------------------------|-----------------------|-----|------|--------------|--|

| Designator | Descriptions                                    | 433.92 MHz 868.35 MHz |     | Unit | Manufacturer |  |

| U1         | CMT2119A, 240 – 960 MHz (G)FSK/OOK transmitter  | -                     |     | -    | CMOSTEK      |  |

| U2         | Optional MCU for on-line register configuration | -                     |     | -    | -            |  |

| X1         | ±20 ppm, SMD32*25 mm crystal                    | 2                     | 6   | MHz  | EPSON        |  |

| C0         | ±20%, 0402 X7R, 25 V                            | 0.                    | .1  | uF   | Murata GRM15 |  |

| C1         | ±5%, 0402 NP0, 50 V                             | 82                    | 82  | pF   | Murata GRM15 |  |

| C2         | ±5%, 0402 NP0, 50 V                             | 9                     | 3.9 | pF   | Murata GRM15 |  |

| L1         | ±5%, 0603 multi-layer chip inductor             | 180                   | 100 | nΗ   | Murata LQG18 |  |

| L2         | ±5%, 0603 multi-layer chip inductor             | 27                    | 8.2 | nΗ   | Murata LQG18 |  |

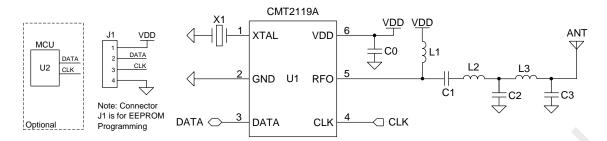

### 4.2 FCC/ETSI Compliant Application Schematic

Figure 10. FCC/ETSI Compliant Application Schematic

#### Notes:

- 1. Connector J1 is a must for the CMT2119A EEPROM access during development or manufacture.

- 2. An external MCU U2 is necessary if on-line register configuration is required.

- 3. The general layout guidelines are listed below. For more design details, please refer to "AN101 CMT211xA Schematic and PCB Layout Design Guideline".

- Use as much continuous ground plane metallization as possible.

- Use as many grounding vias (especially near to the GND pins) as possible to minimize series parasitic inductance between the ground pour and the GND pins.

- Avoid using long and/or thin transmission lines to connect the components.

- Avoid placing the nearby inductors in the same orientation to reduce the coupling between them.

- Place C0 as close to the CMT2119A as possible for better filtering.

- 4. The table below shows the BOM of 433.92/868.35 MHz FCC/ETSI Compliant Application. For the BOM of 315 and 915 MHz application, please refer to "AN101 CMT211xA Schematic and PCB Layout Design Guideline".

Table 8. BOM of 433.92/868.35 MHz FCC/ETSI Compliant Application

| D = -1 === = 1 === | Paradiation                                     | Val        | ue         | l lm!t | Manufacturer |   |  |   |         |

|--------------------|-------------------------------------------------|------------|------------|--------|--------------|---|--|---|---------|

| Designator         | Descriptions                                    | 433.92 MHz | 868.35 MHz | Unit   |              |   |  |   |         |

| U1                 | CMT2119A, 240 – 960 MHz (G)FSK/OOK transmitter  | -          |            | -      |              | - |  | - | CMOSTEK |

| U2                 | Optional MCU for on-line register configuration | -          |            | -      | -            |   |  |   |         |

| X1                 | ±20 ppm, SMD32*25 mm crystal                    | 26         |            | MHz    | EPSON        |   |  |   |         |

| C0                 | ±20%, 0402 X7R, 25 V                            | 0          | .1         | uF     | Murata GRM15 |   |  |   |         |

| C1                 | ±5%, 0402 NP0, 50 V                             | 68         | 68         | pF     | Murata GRM15 |   |  |   |         |

| C2                 | ±5%, 0402 NP0, 50 V                             | 15         | 9.1        | pF     | Murata GRM15 |   |  |   |         |

| С3                 | ±5%, 0402 NP0, 50 V                             | 15         | 8.2        | pF     | Murata GRM15 |   |  |   |         |

| L1                 | ±5%, 0603 multi-layer chip inductor             | 180        | 100        | nΗ     | Murata LQG18 |   |  |   |         |

| L2                 | ±5%, 0603 multi-layer chip inductor             | 36         | 8.2        | nΗ     | Murata LQG18 |   |  |   |         |

| L3                 | ±5%, 0603 multi-layer chip inductor             | 18         | 8.2        | nΗ     | Murata LQG18 |   |  |   |         |

### 5. Functional Descriptions

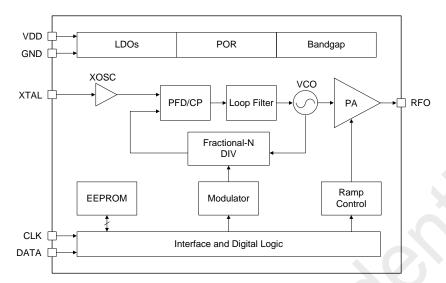

Figure 11. CMT2119A Functional Block Diagram

#### 5.1 Overview

The CMT2119A is a high performance, highly flexible, low-cost, single-chip (G)FSK/OOK transmitter for various 240 to 960 MHz wireless applications. It is part of the CMOSTEK NextGenRF<sup>™</sup> family, which includes a complete line of transmitters, receivers and transceivers. The chip is optimized for the low system cost, low power consumption, battery powered application with its highly integrated and low power design.

The functional block diagram of the CMT2119A is shown in the figure above. The CMT2119A is based on direct synthesis of the RF frequency, and the frequency is generated by a low-noise fractional-N frequency synthesizer. It uses a 1-pin crystal oscillator circuit with the required crystal load capacitance integrated on-chip to minimize the number of external components. Every analog block is calibrated on each Power-on Reset (POR) to the internal voltage reference. The calibration can help the chip to finely work under different temperatures and supply voltages. The CMT2119A uses the DATA pin for the host MCU to send in the data. The input data will be modulated and sent out by a highly efficient PA, which output power can be configured from -10 to +13 dBm in 1 dB step size

The user can directly use the CMT2119A default configuration for immediate demands. If that cannot meet the system requirement, on-line register configuration and off-line EEPROM programming configuration are available for the user to customize the chip features. The on-line configuration means there is an MCU available in the application to configure the chip registers through the 2-wire interface, while the off-line configuration is done by the CMOSTEK USB Programmer and the RFPDK. After the configuration is done, only the DATA pin is required for the host MCU to send in the data and control the transmission. The CMT2119A operates from 1.8 to 3.6 V so that it can finely work with most batteries to their useful power limits. It only consumes 15.5 mA (OOK @ 868.35 MHz) / 27.6 mA (FSK @ 868.35 MHz) when transmitting +10 dBm power under 3.3 V supply voltage.

### 5.2 Modulation, Frequency, Deviation and Symbol Rate

The CMT2119A supports GFSK/FSK modulation with the symbol rate up to 100 ksps, as well as OOK modulation with the symbol rate up to 30 ksps. The supported deviation of the (G)FSK modulation ranges from 1 to 200 kHz. The CMT2119A continuously covers the frequency range from 240 to 960 MHz, including the license free ISM frequency band around 315 MHz, 433.92 MHz, 868.35 MHz and 915 MHz. The device contains a high spectrum purity low power fractional-N frequency synthesizer with output frequency resolution better than 198 Hz when the frequency is less than 480 MHz, and is about 397 Hz

when the frequency is larger than 480 MHz. See the table below for the modulation, frequency and symbol rate specifications.

| Parameter                                        | Value      | Unit |

|--------------------------------------------------|------------|------|

| Modulation                                       | (G)FSK/OOK | -    |

| Frequency                                        | 240 to 960 | MHz  |

| Deviation                                        | 1 to 200   | kHz  |

| Frequency Resolution (F <sub>RF</sub> ≤ 480 MHz) | 198        | Hz   |

| Frequency Resolution (F <sub>RF</sub> > 480 MHz) | 397        | Hz   |

| Symbol Rate (FSK/GFSK)                           | 0.5 to 100 | ksps |

| Symbol Rate (OOK)                                | 0.5 to 30  | ksps |

Table 9. Modulation, Frequency and Symbol Rate

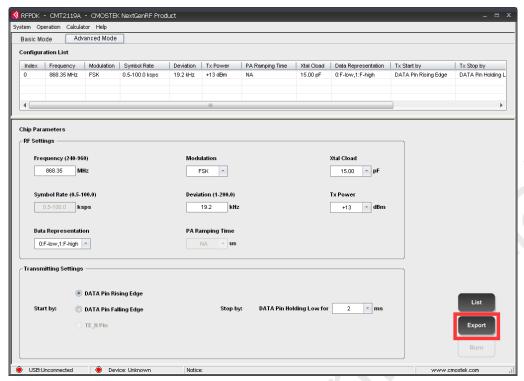

#### 5.3 Embedded EEPROM and RFPDK

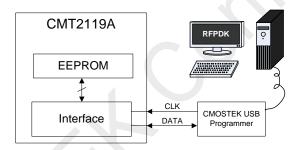

The RFPDK (RF Products Development Kit) is a very user-friendly software tool delivered for the user configuring the CMT2119A in the most intuitional way. The user only needs to fill in/select the proper value of each parameter and click the "Burn" button to complete the chip configuration. See the figure below for the accessing of the EEPROM and Table 10 for the summary of all the configurable parameters of the CMT2119A in the RFPDK.

Figure 12. Accessing Embedded EEPROM

For more details of the CMOSTEK USB Programmer and the RFPDK, please refer to "AN103 CMT211xA-221xA One-Way RF Link Development Kits Users Guide". For the detail of CMT2119A configurations with the RFPDK, please refer to "AN122 CMT2113/19A Configuration Guideline".

**Table 10. Configurable Parameters in RFPDK**

| Category                 | Parameters  | Descriptions                                                                                                                     | Default                              | Mode              |

|--------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-------------------|

|                          | Frequency   | To input a desired transmitting radio frequency in the range from 240 to 960 MHz. The step size is 0.001 MHz.                    | 868.35 MHz                           | Basic<br>Advanced |

|                          | Modulation  | The option is FSK or GFSK and OOK.                                                                                               | FSK                                  | Basic<br>Advanced |

|                          | Deviation   | The FSK frequency deviation. The range is from 1 to 100 kHz.                                                                     | 35 kHz                               | Basic<br>Advanced |

|                          | Symbol Rate | The GFSK symbol rate. The user does not need to specify symbol rate for FSK and OOK modulation.                                  | 2.4 ksps                             | Basic<br>Advanced |

| RF Settings              | Tx Power    | To select a proper transmitting output power from -10 dBm to +14 dBm, 1 dB margin is given above +13 dBm.                        | +13 dBm                              | Basic<br>Advanced |

|                          | Xtal Load   | On-chip XOSC load capacitance options: from 10 to 22 pF. The step size is 0.33 pF.                                               | 15 pF                                | Basic Advanced    |

| Data<br>Representation   |             | To select whether the frequency "Fo + Fdev" represent data 0 or 1. The options are:  0: F-high 1: F-low, or  0: F-low 1: F-high. | 0: F-low<br>1: F-high                | Advanced          |

|                          | PA Ramping  | To control PA output power ramp up/down time for OOK transmission, options are 0 and 2 <sup>n</sup> us (n from 0 to 10).         | 0 us                                 | Advanced          |

| Turner                   | Start by    | Start condition of a transmitting cycle, by Data Pin Rising/Falling Edge.                                                        | Data Pin Rising<br>Edge              | Advanced          |

| Transmitting<br>Settings | Stop by     | Stop condition of a transmitting cycle, by Data Pin Holding Low for 2 to 90 ms.                                                  | Data Pin<br>Holding Low for<br>20 ms | Advanced          |

#### 5.4 On-line Register Configuration

The on-line register configuration means there is an MCU available in the application to configure the chip registers through the TWI: CLK and DATA. The value of the registers, which is originally copied from the EEPROM at the chip's power-up, will remain its value until part or all of the registers are modified by the host MCU. The register value will be lost after the chip's power-down, and re-configuration is necessary when it is powered up again.

For the detail of the on-line register configuration flow, please refer to Chapter 7.

### 5.5 Power Amplifier

A highly efficient single-ended Power Amplifier (PA) is integrated in the CMT2119A to transmit the modulated signal out. Depending on the application, the user can design a matching network for the PA to exhibit optimum efficiency at the desired output power for a wide range of antennas, such as loop or monopole antenna. Typical application schematics and the required BOM are shown in "Chapter 4 Typical Application Schematic". For the schematic, layout guideline and the other detailed information please refer to "AN101 CMT211xA Schematic and PCB Layout Design Guideline".

The output power of the PA can be configured by the user within the range from -10 dBm to +13 dBm in 1 dB step size using the CMOSTEK USB Programmer and RFPDK.

#### 5.6 PA Ramping

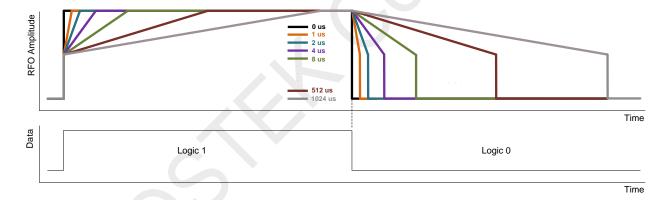

When the PA is switched on or off quickly, its changing input impedance momentarily disturbs the VCO output frequency. This process is called VCO pulling, and it manifests as spectral splatter or spurs in the output spectrum around the desired carrier frequency. By gradually ramping the PA on and off, PA transient spurs are minimized. The CMT2119A has built-in PA ramping configurability with options of 0, 1, 2, 4, 8, 16, 32, 64, 128, 256, 512 and 1024 us, as shown in Figure 13. These options are only available when the modulation type is OOK. When the option is set to "0", the PA output power will ramp up to its configured value in the shortest possible time. The ramp down time is identical to the ramp up time in the same configuration.

CMOSTEK recommends that the maximum symbol rate should be no higher than 1/2 of the PA ramping "rate", as shown in the formula below.

$$SR_{Max} \le 0.5 * \left( \frac{1}{t_{RAMP}} \right)$$

In which the PA ramping "rate" is given by  $(1/t_{RAMP})$ . In other words, by knowing the maximum symbol rate in the application, the PA ramping time can be calculated by formula below.

$$t_{RAMP} \le 0.5 * \left(\frac{1}{SR_{MAX}}\right)$$

The user can select one of the values of the  $t_{RAMP}$  in the available options that meet the above requirement. If somehow the  $t_{RAMP}$  is set to be longer than "0.5 \* (1/SR<sub>Max</sub>)", it will possibly bring additional challenges to the OOK demodulation of the Rx device. For more detail of calculating  $t_{RAMP}$ , please refer to "AN122 CMT2113/19A Configuration Guideline".

Figure 13. PA Ramping Time

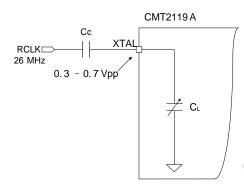

### 5.7 Crystal Oscillator and RCLK

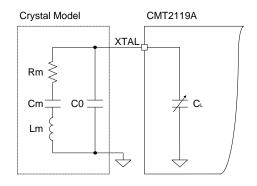

The CMT2119A uses a 1-pin crystal oscillator circuit with the required crystal load capacitance integrated on-chip. Figure 14 shows the configuration of the XTAL circuitry and the crystal model. The recommended specification for the crystal is 26 MHz with  $\pm$ 20 ppm, ESR (Rm) < 60  $\Omega$ , load capacitance C<sub>LOAD</sub> ranging from 12 to 20 pF. To save the external load capacitors, a set of variable load capacitors C<sub>L</sub> is built inside the CMT2119A to support the oscillation of the crystal.

The value of load capacitors is configurable with the CMOSTEK USB Programmer and RFPDK. To achieve the best performance, the user only needs to input the desired value of the XTAL load capacitance  $C_{LOAD}$  of the crystal (can be found in the datasheet of the crystal) to the RFPDK, then finely tune the required XO load capacitance according to the actual XO frequency. Please refer to "AN103 CMT211xA-221xA One-Way RF Link Development Kits Users Guide" for the method of choosing the right value of  $C_L$ .

Figure 14. XTAL Circuitry and Crystal Model

Figure 15. RCLK Circuitry

If a 26 MHz RCLK (reference clock) is available in the system, the user can directly use it to drive the CMT2119A by feeding the clock into the chip via the XTAL pin. This further saves the system cost due to the removal of the crystal. A coupling capacitor is required if the RCLK is used. The recommended amplitude of the RCLK is 0.3 to 0.7 Vpp on the XTAL pin. Also, the user should set the internal load capacitor  $C_L$  to its minimum value. See Figure 15 for the RCLK circuitry.

### 6. Working States and Transmission Control Interface

### 6.1 Working States

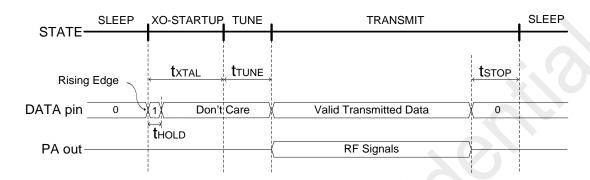

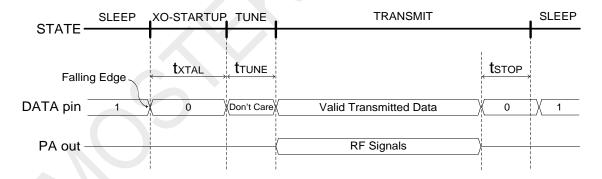

The CMT2119A has following 4 different working states: SLEEP, XO-STARTUP, TUNE and TRANSMIT.

#### **SLEEP**

When the CMT2119A is in the SLEEP state, all the internal blocks are turned off and the current consumption is minimized to 20 nA typically.

#### **XO-STARTUP**

After detecting a valid control signal on DATA pin, the CMT2119A goes into the XO-STARTUP state, and the internal XO starts to work. The valid control signal can be a rising or falling edge on the DATA pin, which can be configured on the RFPDK. The host MCU has to wait for the  $t_{XTAL}$  to allow the XO to get stable. The  $t_{XTAL}$  is to a large degree crystal dependent. A typical value of  $t_{XTAL}$  is provided in the Table 11.

#### **TUNE**

The frequency synthesizer will tune the CMT2119A to the desired frequency in the time  $t_{TUNE}$ . The PA can be turned on to transmit the incoming data only after the TUNE state is done, before that the incoming data will not be transmitted. See Figure 16 and Figure 17 for the details.

#### **TRANSMIT**

The CMT2119A starts to modulate and transmit the data coming from the DATA pin. The transmission can be ended in 2 methods: firstly, driving the DATA pin low for  $t_{STOP}$  time, where the  $t_{STOP}$  can be configured from 20 to 90 ms on the RFPDK; secondly, issuing SOFT\_RST command over the two-wire interface, this will stop the transmission in 1 ms. See Section 6.2.3 for details of the two-wire interface.

| T-11- | 44     |            | D:((      | <b>AA/</b> | 01-1   |

|-------|--------|------------|-----------|------------|--------|

| Iania | าา เเก | ina in     | Different | WARKINA    | STOTE  |

| Iabic | 4 1    | IIII M III | DILLETELL | VVOIRIII   | Julian |

| Parameter                                    | Symbol            | Min | Тур | Max | Unit |

|----------------------------------------------|-------------------|-----|-----|-----|------|

| XTAL Startup Time [1]                        | t <sub>XTAL</sub> |     | 400 |     | us   |

| Time to Tune to Desired Frequency            | t <sub>TUNE</sub> |     | 370 |     | us   |

| Hold Time After Rising Edge                  | t <sub>HOLD</sub> | 10  |     |     | ns   |

| Time to Stop the Transmission <sup>[2]</sup> | t <sub>STOP</sub> | 2   |     | 90  | ms   |

#### Notes:

- [1]. This parameter is to a large degree crystal dependent.

- [2]. Configurable from 2 to 9 in 1 ms step size and 20 to 90 ms in 10 ms step size.

#### **6.2 Transmission Control Interface**

The CMT2119A uses the DATA pin for the host MCU to send in data for modulation and transmission. The DATA pin can be used as pin for EEPROM programming, data transmission, as well as controlling the transmission. The transmission can be started by detecting rising or falling edge on the DATA pin, and stopped by driving the DATA pin low for t<sub>STOP</sub> as shown in the table above. Besides communicating over the DATA pin, the host MCU can also communicate with the device over the two-wire interface, so that the transmission is more robust, and consumes less current.

Please note that the user is recommended to use the Tx Enabled by DATA pin Rising Edge, which is described in Section 6.2.1.

#### 6.2.1 Tx Enabled by DATA Pin Rising Edge

As shown in the figure below, once the CMT2119A detects a rising edge on the DATA pin, it goes into the XO-STARTUP state. The user has to pull the DATA pin high for at least 10 ns  $(t_{HOLD})$  after detecting the rising edge, as well as wait for the sum of  $t_{XTAL}$  and  $t_{TUNE}$  before sending any useful information (data to be transmitted) into the chip on the DATA pin. The logic state of the DATA pin is "Don't Care" from the end of  $t_{HOLD}$  till the end of  $t_{TUNE}$ . In the TRANSMIT state, PA sends out the input data after they are modulated. The user has to pull the DATA pin low for  $t_{STOP}$  in order to end the transmission.

Figure 16. Transmission Enabled by DATA Pin Rising Edge

#### 6.2.2 Tx Enabled by DATA Pin Falling Edge

As shown in the figure below, once the CMT2119A detects a falling edge on the DATA pin, it goes into XO-STARTUP state and the XO starts to work. During the XO-STARTUP state, the DATA pin needs to be pulled low. After the XO is settled, the CMT2119A goes to the TUNE state. The logic state of the DATA pin is "Don't Care" during the TUNE state. In the TRANSMIT state, PA sends out the input data after they are modulated. The user has to pull the DATA pin low for t<sub>STOP</sub> in order to end the transmission. Before starting the next transmit cycle, the user has to pull the DATA pin back to high.

Figure 17. Transmission Enabled by DATA Pin Falling Edge

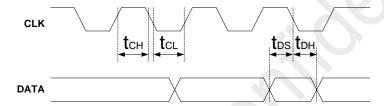

#### 6.2.3 Two-wire Interface

For power-saving and reliable transmission purposes, the CMT2119A is recommended to communicate with the host MCU over a two-wire interface (TWI): DATA and CLK. The TWI is designed to operate at a maximum of 1 MHz. The timing requirement and data transmission control through the TWI are shown in this section.

| <b>Table</b> | 12. | TWI | Requirements |

|--------------|-----|-----|--------------|

|--------------|-----|-----|--------------|

| Parameter                | Symbol           | Conditions                                                                                                    | Min | Тур | Max    | Unit     |

|--------------------------|------------------|---------------------------------------------------------------------------------------------------------------|-----|-----|--------|----------|

| Digital Input Level High | V <sub>IH</sub>  |                                                                                                               | 0.8 |     |        | $V_{DD}$ |

| Digital Input Level Low  | V <sub>IL</sub>  |                                                                                                               |     |     | 0.2    | $V_{DD}$ |

| CLK Frequency            | F <sub>CLK</sub> |                                                                                                               | 10  |     | 1,000  | kHz      |

| CLK High Time            | t <sub>CH</sub>  |                                                                                                               | 500 |     |        | ns       |

| CLK Low Time             | t <sub>CL</sub>  |                                                                                                               | 500 |     |        | ns       |

| CLK Delay Time           | t <sub>CD</sub>  | CLK delay time for the first falling edge of the TWI_RST command, see Figure 20                               | 20  |     | 15,000 | ns       |

| DATA Delay Time          | t <sub>DD</sub>  | The data delay time from the last CLK rising edge of the TWI command to the time DATA return to default state |     | *   | 15,000 | ns       |

| DATA Setup Time          | t <sub>DS</sub>  | From DATA change to CLK falling edge                                                                          | 20  |     |        | ns       |

| DATA Hold Time           | t <sub>DH</sub>  | From CLK falling edge to DATA change                                                                          | 200 |     |        | ns       |

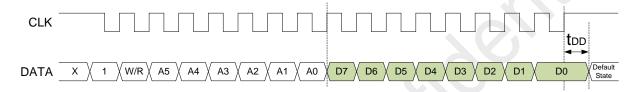

Figure 18. Two-wire Interface Timing Diagram

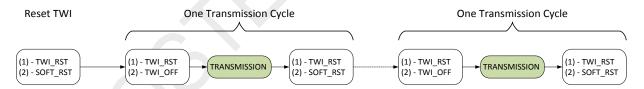

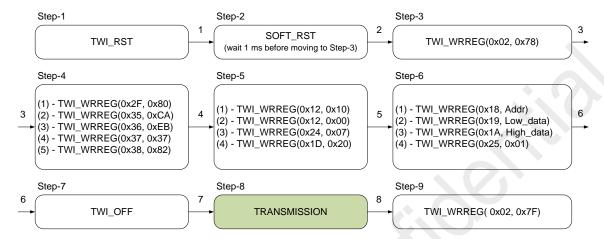

Once the device is powered up, TWI\_RST and SOFT\_RST should be issued to make sure the device works in SLEEP state robustly. On every transmission, TWI\_RST and TWI\_OFF should be issued before the transmission to make sure the TWI circuit functions correctly. TWI\_RST and SOFT\_RST should be issued again after the transmission for the device going back to SLEEP state reliably till the next transmission. The operation flow with TWI is shown as the figure below.

Figure 19. CMT2119A Operation Flow with TWI

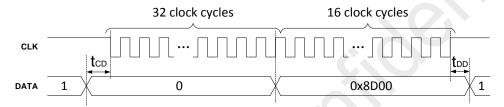

**Table 13. TWI Commands Descriptions**

| Command | Descriptions                                                                                                  |  |  |  |  |  |  |

|---------|---------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|         | Implemented by pulling the DATA pin low for 32 clock cycles and clocking in 0x8D00, 48 clock cycles in total. |  |  |  |  |  |  |

|         | It only resets the TWI circuit to make sure it functions correctly. The DATA pin cannot detect the            |  |  |  |  |  |  |

|         | Rising/Falling edge to trigger transmission after this command, until the TWI_OFF command is issued.          |  |  |  |  |  |  |

| TWI_RST |                                                                                                               |  |  |  |  |  |  |

| _       | Notes:                                                                                                        |  |  |  |  |  |  |

|         | Please ensure the DATA pin is firmly pulled low during the first 32 clock cycles.                             |  |  |  |  |  |  |

|         | 2. When the device is configured as Transmission Enabled by DATA Pin Falling Edge, in order to issue          |  |  |  |  |  |  |

|         | the TWI_RST command correctly, the first falling edge of the CLK should be sent tcD after the DATA            |  |  |  |  |  |  |

|         | falling edge, which should be longer than the minimum DATA setup time 20 ns, and shorter than 15 us,          |  |  |  |  |  |  |

| Command  | Descriptions                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|          | as shown in Figure 20.                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|          | 3. When the device is configured as Transmission Enabled by DATA Pin Rising Edge, the default state of                                                                                                                                                                                                                                       |  |  |  |  |

|          | the DATA is low, there is no $t_{CD}$ requirement, as shown in Figure 21.                                                                                                                                                                                                                                                                    |  |  |  |  |

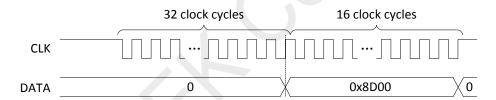

|          | Implemented by clocking in 0x8D02, 16 clock cycles in total.                                                                                                                                                                                                                                                                                 |  |  |  |  |

| TWI_OFF  | It turns off the TWI circuit, and the DATA pin is able to detect the Rising/Falling edge to trigger transmission after this command, till the TWI_RST command is issued. The command is shown as Figure 22.                                                                                                                                  |  |  |  |  |

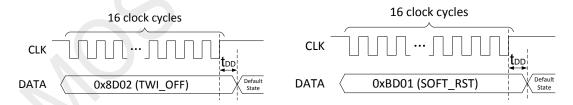

|          | Implemented by clocking in 0xBD01, 16 clock cycles in total.                                                                                                                                                                                                                                                                                 |  |  |  |  |

| SOFT_RST | FT_RST  It resets all the other circuits of the chip except the TWI circuit. This command will trigger internal calib for getting the optimal device performance. After issuing the SOFT_RST command, the host MCU sho wait 1 ms before sending in any new command. After that, the device goes to SLEEP state. The comm shown as Figure 23. |  |  |  |  |

Figure 20. TWI\_RST Command When Transmission Enabled by DATA Pin Falling Edge

Figure 21. TWI\_RST Command When Transmission Enabled by DATA Pin Rising Edge

Figure 22. TWI\_OFF Command

Figure 23. SOFT\_RST Command

The DATA is generated by the host MCU on the rising edge of CLK, and is sampled by the device on the falling edge. The CLK should be pulled up by the host MCU during the TRANSMISSION shown in Figure 19. The TRANSMISSION process should refer to Figure 16 or Figure 17 for its timing requirement, depending on the "Start By" setting configured on the RFPDK.

The device will go to SLEEP state by driving the DATA low for  $t_{STOP}$ , or issuing SOFT\_RST command. A helpful practice for the device to go to SLEEP is to issue TWI\_RST and SOFT\_RST commands right after the useful data is transmitted, instead of waiting the  $t_{STOP}$ , this can save power significantly.

### 7. On-Line Register Configuration Flow

Besides off-line EEPROM programming to tailor the chip features, on-line register configuration through the two-wire interface can do the work in another way, which is mentioned in Section 5.4. This chapter gives more details on accessing chip registers with TWI.

### 7.1 Accessing Registers with TWI

The TWI includes an input port CLK and a bi-directional port DATA. A complete Write/Read (W/R) process has 16 clock cycles. For the first 8 clock cycles, the DATA is used as input port for writing register address; and for the last 8 clock cycles, the DATA is used as input port during write process, and output port during read process. The timing chart for the TWI W/R is shown as the figure below. Please note that the TWI\_RST command is a special command which does not apply to the guidelines introduced below. The TWI\_RST command is introduced in Table 13, Figure 20 and Figure 21in details.

Figure 24. TWI W/R Timing Chart (Except for TWI\_RST Command)

#### Notes:

- 1. The timing requirement is shown as Table 12.

- 2. At the end of each command, the DATA should return to its default state after the last CLK rising edge within the time tpd.

- 3. The command always start with "1", the first 8 clock cycle includes the W/R control and address bits A[5:0]. It is a Read command when W/R is 1, and Write command when W/R is 0. The range of the address bits is from 0x00 to 0x3F.

- 4. In a Write command, D[7:0] is the data to be written into the register. In a Read command, D[7:0] is the data to be read from the register.

- 5. The DATA pin is a bi-directional port, and it will be switched to output port in the last 8 clock cycle of a Read command. At this time, the host MCU should switch the corresponding port which is connected to the DATA pin to input port at the coming CLK rising edge, shown as dash line in the middle of Figure 24, so that there is no voltage conflict between the two ports and the read out function is correctly behaved.

- 6. To simplify the expression, this datasheet is using the TWI\_WRREG and TWI\_RDREG to represent the write and read command to specified registers, as shown in the table below.

|           | Table 14.1 WI_WRKEG and TWI_RDREG                                                                                                                                                                                                                       |  |  |  |  |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Command   | Description                                                                                                                                                                                                                                             |  |  |  |  |

| TWI_WRREG | TWI write command. TWI_WRREG(XX, YY) means clocking in 16b'10xx xxxx yyyy yyyy, which xx xxxx is the register address to be written, ranging from 0x00 to 0x3F; yyyy yyyy is the register content to be written ranging from 0x00 to 0xFF.              |  |  |  |  |

|           | For example, TWI_WRREG(0x12, 0xAA) means clocking in 0x92AA.                                                                                                                                                                                            |  |  |  |  |

| TWI_RDREG | TWI read command, TWI_RDREG(XX, ZZ) means clocking in 8b'11xx xxxx and read out zzzz zzzz, which xx xxxx is the register address to be written, ranging from 0x00 to 0x3F; zzzz zzzz is the read out value from the register, ranging from 0x00 to 0xFF |  |  |  |  |

|           | For example, TWI_RDREG(0x2A, DAT), means clocking in 0xEA, and read out DAT which is an 8-bit value.                                                                                                                                                    |  |  |  |  |

Table 14.TWI WRREG and TWI RDREG

7. Specific commands TWI\_RST, TWI\_OFF and SOFT\_RST are also used in the on-line register configuration, refer to Table 13 for the definition of the 3 commands.

### 7.2 Configuration Flow

The user should follow below flow chart for the on-line register configuration.

Figure 25. On-line Register Configuration Flow

#### Notes:

- 1. In step-2, the host MCU issues the SOFT\_RST command and needs to wait 1 ms before moving to step-3.

- 2. The feature registers are 16-bit wide, which address is indicated as Addr in step-6. The host MCU needs to first write the Addr to register 0x18. After that, the host MCU divides the feature register content into two 8-bit parts: Low\_data and High\_data, then write them into two temporary registers, which addresses are 0x19 and 0x1A, and finally overwrite the target 16-bit register by issuing TWI\_WRREG(0x25, 0x1) to complete the feature register writing, as shown in step-6. Repeat step-6 if multiple feature registers are need to configured.

For example, if the user wants to write 0xC3F6 to feature register which address is 0x02, the user should issue the commands shown in step-6, and listed as below.

```

a) TWI_WRREG(0x18, 0x02); // Write the Addr 0x02 to register 0x18

b) TWI_WRREG(0x19, 0xF6); // Write the Low_data 0xF6 to register 0x19

c) TWI_WRREG(0x1A, 0xC3); // Write the High_data 0xC3 to register 0x1A

d) TWI_WRREG(0x25, 0x01); // Trigger the overwriting to the feature register, the writing process completes

```

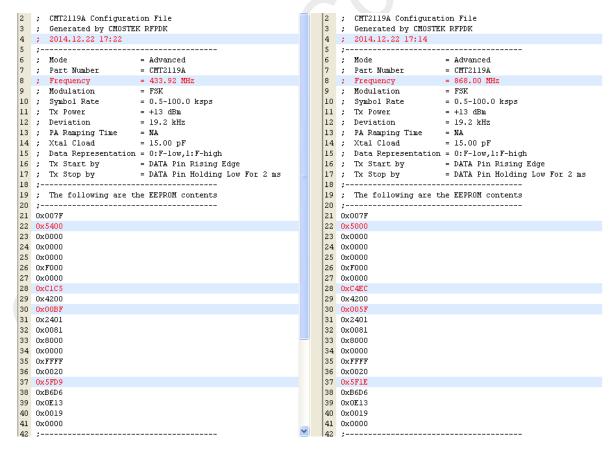

- 3. As a specific feature could be related to several registers, in order to change the feature correctly, the user is recommended to find out the corresponding registers by Export function on the RFPDK, as shown in Figure 26. For more RFPDK details, refer to "AN103 CMT211xA-221xA One-Way RF Link Development Kits Users Guide". An example of changing the frequency from 433.92 MHz to 868 MHz is listed below.

- a) Configure the device to work in 433.92 MHz, use the Export function on the RFPDK to generate the configuration file named as 433.92MHz.exp.

- b) Configure the device to work in 868 MHz, generate the configuration file named as 868MHz.exp in the same way.

- c) Compare the 868MHz.exp file with the 433.92MHz.exp file and find out the registers being changed, as shown in Figure 27. Please note that the address of the registers starts from 0x00 and ends at 0x15 (21 registers in total).

- d) Apply the corresponding register value and address in the flow shown in Figure 25.

Figure 26. Export Button on the RFPDK

Figure 27. Examples of Changing Frequency

## 8. Ordering Information

**Table 15. CMT2119A Ordering Information**

| Part Number                 | Descriptions                          | Package<br>Type | Package<br>Option | Operating<br>Condition       | MOQ /<br>Multiple |

|-----------------------------|---------------------------------------|-----------------|-------------------|------------------------------|-------------------|

| CMT2119A-ESR <sup>[1]</sup> | 240-960 MHz (G)FSK/OOK<br>Transmitter | SOT23-6         | Tape & Reel       | 1.8 to 3.6 V,<br>-40 to 85 ℃ | 3,000             |

#### Notes:

Visit www.cmostek.com/products to know more about the product and product line.

$\textbf{Contact} \ \underline{\textbf{sales@cmostek.com}} \ \textbf{or your local sales representatives for more information}.$

<sup>[1]. &</sup>quot;E" stands for extended industrial product grade, which supports the temperature range from -40 to +85  $^{\circ}$ C. "S" stands for the package type of SOT23-6 for this product.

<sup>&</sup>quot;R" stands for the tape and reel package option, the minimum order quantity (MOQ) for this option is 3,000 pieces.

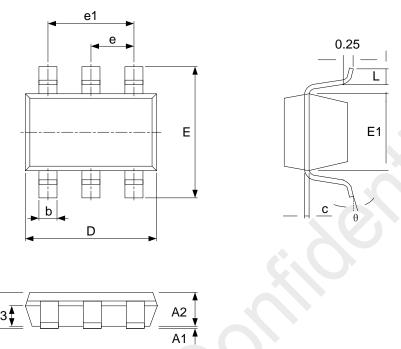

## 9. Package Outline

The 6-pin SOT23-6 illustrates the package details for the CMT2119A. The table below lists the values for the dimensions shown in the illustration.

Figure 28. 6-Pin SOT23-6

Table 16. 6-Pin SOT23-6 Package Dimensions

|        |          | Size (millimeters) |      |  |

|--------|----------|--------------------|------|--|

| Symbol | Min      | Тур                | Max  |  |

| А      | _        | _                  | 1.35 |  |

| A1     | 0.04     | _                  | 0.15 |  |

| A2     | 1.00     | 1.10               | 1.20 |  |

| A3     | 0.55     | 0.65               | 0.75 |  |

| b      | 0.38     | _                  | 0.48 |  |

| С      | 0.08     | _                  | 0.20 |  |

| D      | 2.72     | 2.92               | 3.12 |  |

| E      | 2.60     | 2.80               | 3.00 |  |

| E1     | 1.40     | 1.60               | 1.80 |  |

| е      | 0.95 BSC |                    |      |  |

| e1     | 1.90 BSC |                    |      |  |

| L      | 0.30     | _                  | 0.60 |  |

| θ      | 0        | _                  | 8°   |  |

## 10. Top Marking

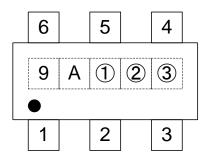

### 10.1 CMT2119A Top Marking

Figure 29. CMT2119A Top Marking

Table 17. CMT2119A Top Marking Explanation

| Top Mark                                 | 9A①②③                                                                          |

|------------------------------------------|--------------------------------------------------------------------------------|

| Mark Method                              | Laser                                                                          |

| Font Size                                | 0.6 mm, right-justified                                                        |

| 1 <sup>st</sup> letter                   | 9, represents CMT2119                                                          |

| 2 <sup>nd</sup> letter                   | A: represents revision A                                                       |

| 3 <sup>rd</sup> – 5 <sup>th</sup> letter | ①②③: Internal reference for data code tracking, assigned by the assembly house |

### 11. Other Documentations

Table 18. Other Documentations for CMT2119A

| Brief | Name                                                        | Descriptions                                                                                                                              |

|-------|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| AN101 | CMT211xA Schematic and PCB Layout Design Guideline          | Details of CMT211xA PCB schematic and layout design rules, RF matching network and other application layout design related issues.        |

| AN122 | CMT2113/19A Configuration Guideline                         | Details of configuring CMT2113/19A features on the RFPDK, and the on-line configuration guideline for CMT2119A.                           |

| AN103 | CMT211xA-221xA One-Way RF Link Development Kits Users Guide | User's Guides for CMT211xA/CMT221xA Development Kits, including Evaluation Board and Evaluation Module, CMOSTEK USB Programmer and RFPDK. |

## 12. Document Change List

**Table 19. Document Change List**

| Rev. No. | Chapter | Description of Changes         | Date       |

|----------|---------|--------------------------------|------------|

| 0.6      | All     | Initial Released               | 2014-12-05 |

| 0.8      | 6, 7    | Adding Chapter 6 and Chapter 7 | 2015-01-16 |

| 0.9      | 6       | Update Section 6.2.3           | 2015-01-23 |

#### 13. Contact Information

CMOSTEK Microelectronics Co., Ltd.

Room 202, Honghai Building, Qianhai Road. Nanshan District

Shenzhen, Guangdong, China PRC

Zip Code: 518000 Tel: 0755 - 83235017 Fax: 0755 - 82761326 Sales: sales@cmostek.com

Technical support: <a href="mailto:support@cmostek.com">support@cmostek.com</a>

www.cmostek.com

#### Copyright. CMOSTEK Microelectronics Co., Ltd. All rights are reserved.

The information furnished by CMOSTEK is believed to be accurate and reliable. However, no responsibility is assumed for inaccuracies and specifications within this document are subject to change without notice. The material contained herein is the exclusive property of CMOSTEK and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of CMOSTEK. CMOSTEK products are not authorized for use as critical components in life support devices or systems without express written approval of CMOSTEK. The CMOSTEK logo is a registered trademark of CMOSTEK Microelectronics Co., Ltd. All other names are the property of their respective owners.